ニュース

インテル,Sandy Bridgeのアーキテクチャを日本語で詳しく解説

|

本稿ではそのなかから,次世代CPU「Sandy Bridge」(サンディブリッジ,開発コードネーム)に関する話題を中心にまとめてみたいと思う。

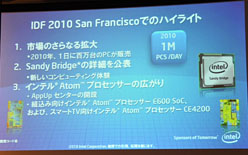

吉田氏はIDF 2010 SFを振り返り,Sandy Bridgeに関する詳細が明らかになったことと,北米におけるAppUpストアの立ち上がりなど,Atomプロセッサの市場が広がっていることを強調 |

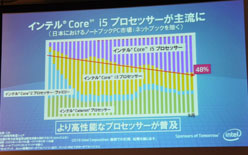

Core i5&i3プロセッサの順調なシェアの拡大をアピールする吉田氏。日本のノートPC市場ではすでにCore i5搭載機のシェアが50%に迫り,Core i3搭載モデルと合わせると80%近いとした |

「シームレスなビジュアル体験の実現」

を目指すSandy Bridge

|

→IDF 2010 SFレポート:Sandy Bridgeのアーキテクチャ

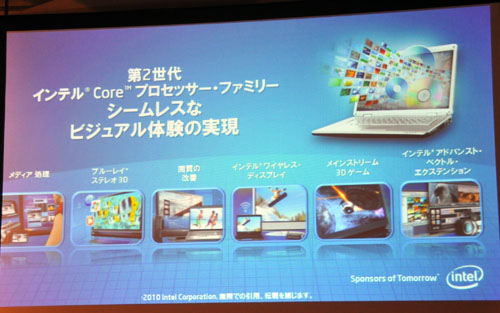

さて,土岐氏は,Sandy Bridgeのキーワードを「シームレスなビジュアル体験の実現」という言葉で紹介した。これが,日本におけるSandy Bridgeの訴求ポイントになるということなのだろう。

下に示したスライドは,「インテルとして,『(PCの)ユーセージがこういう方向に向かっていくだろう』と考えているもの」(土岐氏)。注目したいのは,ここには「メインストリームの3Dゲーム」が含まれていることだ。“インテル語”の「メインストリーム」は,要するに「エントリー」とか「カジュアル」といった意味だが,そのあたりのゲームまではカバーする気満々ということになる。

|

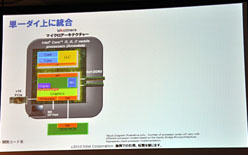

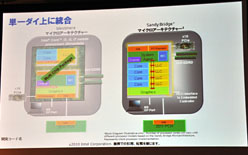

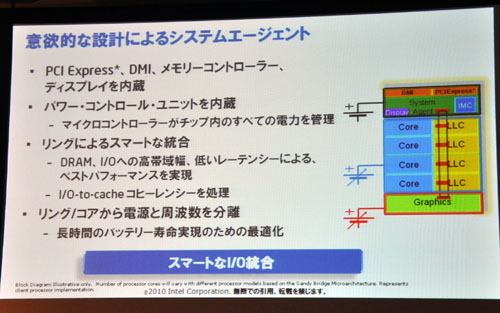

続けて土岐氏が示したのは,Sandy Bridgeでの改良点をまとめたもの。現行製品であるWestmere世代のグラフィックス機能統合型CPUだと,パッケージ上にCPUダイと,いわゆるGMCH(=ノースブリッジ)機能のダイが並ぶ,マルチダイ構造になっていたが,Sandy Bridgeではこれらが1つのダイに集積されるのが大きな特徴となる。Westmere世代からさらに一歩,組み込み分野向けのSoC(System-on-a-Chip)に近づいたといえるかもしれない。

|

|

|

土岐氏はSandy Bridgeで改良された点を順に説明していった。

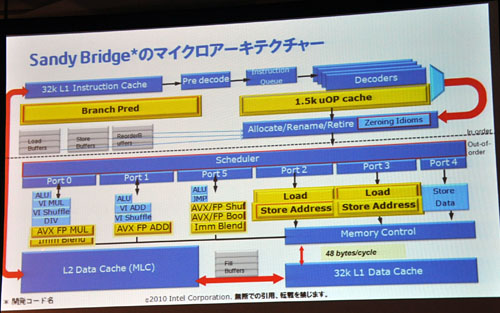

下のスライドは,Sandy BridgeにおけるCPUコアのマイクロアーキテクチャである。黄色い部分が改良点だが,Westmere世代で,メモリから値を読んだり書いたりするロードユニットとストアユニットはそれぞれ1基だったのに対し,Sandy Bridgeではロード/ストアユニット2基+データ専用ストアユニット1基へと拡張されているのは,大きなポイントとなるかもしれない。Sandy Bridge世代で追加される新命令「AVX」(Intel Advanced Vector eXtentions)が256bitのレジスタを使用するため,大きな単位のロードとストアが発生することはもちろん,そもそもx86命令セットはロード&ストアが頻発しやすいということもあるので,パフォーマンスの向上に直結しやすい改良だろうと思う。

|

統合されるグラフィックス機能の性能向上も,Sandy Bridgeにおけるトピックの1つだ。

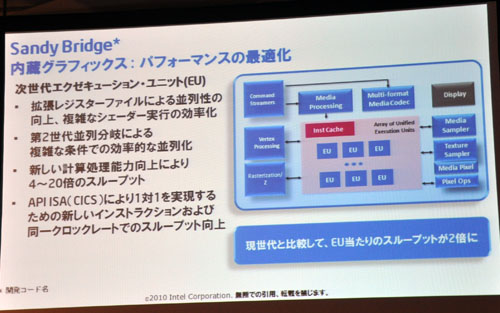

下に示したスライドにあるとおり,複雑なシェーダの実行が高速化されているなど,3Dグラフィックス性能の向上に直結する改良に加え,実行ユニット(EU,Execution Unit)そのものも「APIとインストラクション(=命令)を1対1対応にすることで,従来比で2倍のスループットになっている」(土岐氏)という。

|

ただし,EUの数については「知っているのだが(笑),現時点では言えない」とのことで,まだまだ公表できない部分があることを窺わせていた。Westmere世代と比べて減ることはさすがにないと思われるが,EUが何基あるのかによってグラフィックスの性能は大きく変わるだろう。そもそも,製品シリーズでEUの数が異なる可能性もあるはずで,気になるところだ。

|

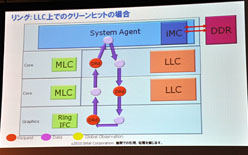

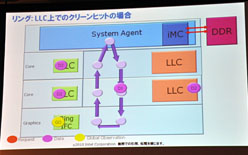

グラフィックス機能がキャッシュへ高速にアクセスできることによる速度面でのメリットはもちろん,「キャッシュにヒットすれば外(=メインメモリ)に行く必要がないので,メモリアクセスの効率が上がる」(土岐氏)といった恩恵も期待できよう。

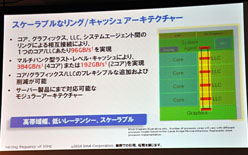

「山手線と違って,片方向のみになる」(土岐氏)Sandy Bridgeのリングバスで,データは基本的に1方向にしか動かない。そのため,ワーストケースでの効率は悪そうに思えるが,その点,Sandy Bridgeでは,LLC(など)に2つの出入り口を持ち,最短経路を通ることができるようになっているとのこと。模式図でハシゴのようになっているのは,そういう意味なのだ。

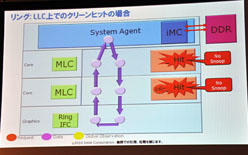

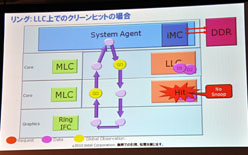

土岐氏は「リングバスがどう動くのか」も示したので,以下,簡単にまとめてみたい。

|

|

|

|

|

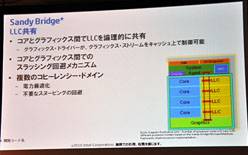

なお,LLCはCPUコアごとのブロックで管理されてはいるものの,リングバスで結ばれて緊密に連携しているため,各キャッシュが同じデータを持とうとする現象である「スラッシング」の回避や,高度なコヒーレンシ(coherency,首尾一貫性。ここではキャッシュとメモリの内容に一貫性を保つこと)を実現していると,土岐氏は述べていた。

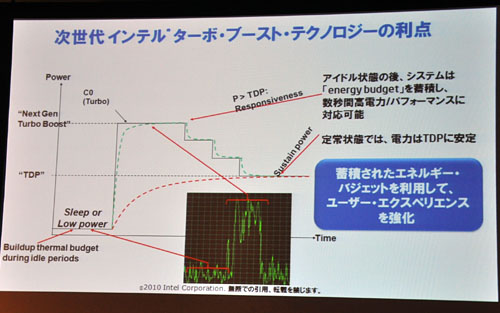

パフォーマンスに関して,もうひとつ大きなトピックになりそうなのが次世代の「Intel Turbo Boost Technology」(以下,Turbo Boost)である。

土岐氏はこれを「冷えているものが暖まるのには時間がかかる。これを応用しようというもの」と説明していた。CPUはアイドル状態が続いている限り,十分低い温度にある。だから,立ち上がりに大きな負荷がかかったときには,TDP(Thermal Design Power,熱設計消費電力)の枠を超える電流量を流し(て,より高い動作クロックに設定し)ても,元が“冷えている”から,発熱的には問題ない,という理屈である。

|

(アイドル状態から)アプリケーションを立ち上げるとき,規定値を大きく超えたクロックで動作することになるため,「体感のレスポンスを大きく改善すると見ている」(土岐氏)とのことだ。

|

以上,土岐氏の解説は非常に分かりやすく,2011年1月にも登場すると見られるSandy Bridgeの登場に向けて,日本法人側の準備はほぼ整ってきたという印象を受けた。予定どおりだとすればあと約1四半期。登場を楽しみに待ちたいところだ。

- 関連タイトル:

Core i7・i5・i3-2000番台(Sandy Bridge)

Core i7・i5・i3-2000番台(Sandy Bridge) - この記事のURL:

(C)Intel Corporation