ニュース

AMD,次世代Radeonで採用する積層メモリ技術「HBM」を解説。キーワードは「高性能&低消費電力」

|

GDDR5の実装面積&消費電力問題を解決するHBM

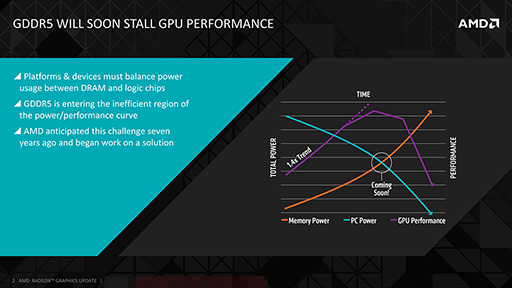

Macri氏は,HBMとは何かを説明する前に,HBMが必要とされる背景として「実装面積」と「電力性能比」の問題があると述べた。

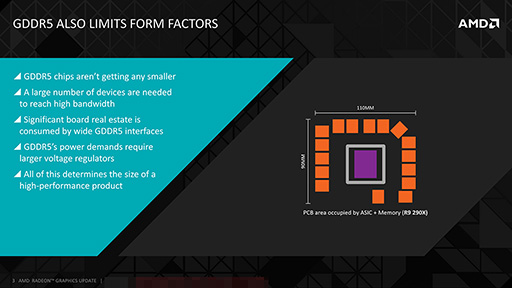

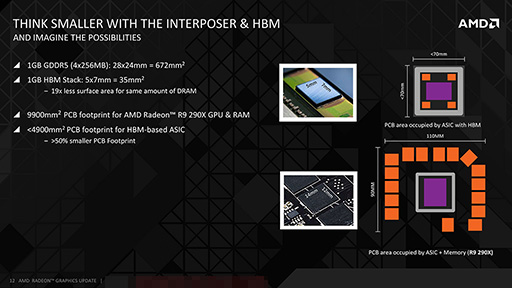

下に示したスライドで右に見えるのは,「Radeon R9 290X」(以下,R9 290X)のリファレンスデザインにおける,GPUとGDDR5メモリの実装を示した模式図だ。図が小さいので,拡大しないと分かりにくいかもしれないが,R9 290Xでは,DRAMチップ16枚で合計容量4GBを実現するにあたって,110×90mmものスペースが必要になるという。そもそも16枚あるメモリチップの占有する面積が大きいだけでなく,GDDR5メモリチップとGPUとの間を広帯域幅のバスで結ばなければならないことが,実装面積上の不利となるのだ。

さらに,GDDR5メモリチップとGPU間の距離を物理的に離さざるを得ないため,信号の振幅を十分に取る必要が生じ,いきおい,動作電圧が高くなって,消費電力が増大することになる。

|

そのため,いずれGDDR5メモリがGPU性能向上の妨げになるというのがMacri氏の予測だ。とくに,動作電圧を下げられないことによる消費電力の増大が,性能の抑制要因になるとのことだった。

その解決策としてAMDが提案するのが,「以前から取り組んできた」(Macri氏)というHBMである。HBMは,2016年に登場予定となっているNVIDIAの次世代GPU「Pascal」(パスカル,開発コードネーム)でも採用される予定だが,それに先駆けて,AMDが採用することになるわけだ。

|

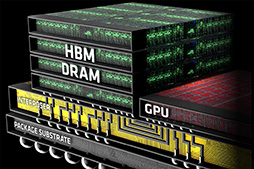

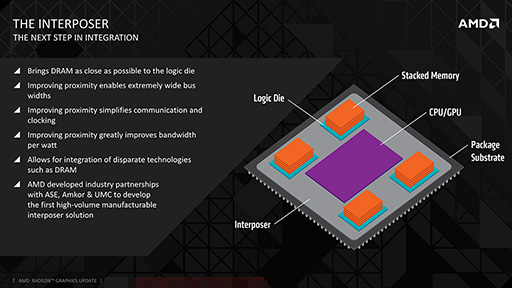

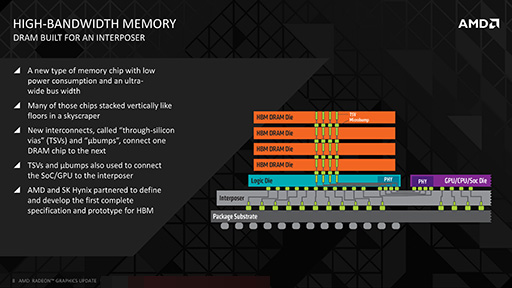

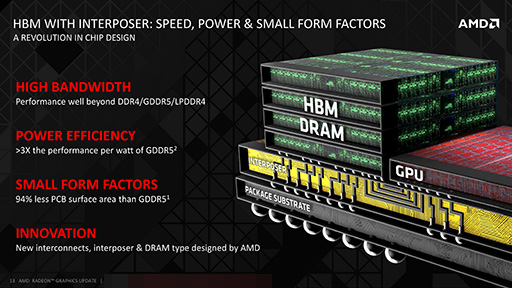

さて,下のスライドで右に見えるのは,AMDの次世代GPUで採用されるHBMの実装を,斜め上から見た模式図となる。プロセッサパッケージの四隅に積み上げられているオレンジのブロックがグラフィックスメモリチップで,メモリインタフェースが実装されたシリコンチップ「Logic Die」(ロジックダイ)の上に「Stacked Memory」(スタックドメモリ,以下 積層メモリ)として積み上げられているのが分かるだろう。

Logic Dieの下には,各Logic DieとGPU,そして,基板と接続される端子への配線が組み込まれた「Interposer」(インターポーザ)があり,それが全体の土台となるパッケージ基板(※図中「Package Substrate」)に載る構造だ。

|

続いて下のスライドにおける右の模式図は,積み上げられたメモリチップの断面を示したものになる。

メモリチップには,メモリインタフェースを縦方向につなぐ「TSV」(Through-Silicon Via,シリコン貫通ビア)が組み込まれ,小型端子「Microbump」(マイクロバンプ。「μbump」と書くこともある)を通じて接続される。こうして積み上げられたメモリチップの下にLogic Die,Interposer,パッケージ基板が配置されるという多層構造になっているわけだ。

|

上の図では接続の概略も記されているのだが,これはかなり大雑把なものであり,実際には,GPUとAPUなど,最終製品によって接続方法は大きく変わるはずだ。今回,そこまで細かい内容は明らかになっていないのだが,Interposerを介してプロセッサとメモリチップが接続され,メモリチップ側にLogic Dieが用意されるデザインから推測するに,GPUと積層メモリ間は,専用の高速バスで接続されるのではなかろうか。

なお,Macri氏によると,HBMの量産技術は,LSIの実装を手がける台湾Ad

HBMの採用で実装面積は従来比わずか5%に!

メモリバス帯域幅も3倍以上

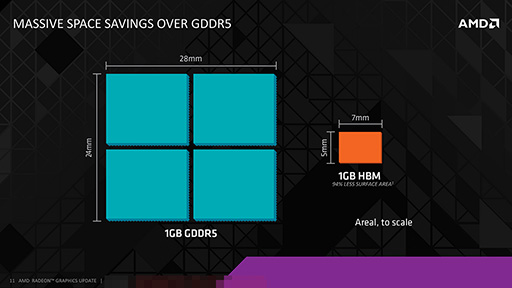

Macri氏は,HBM技術の採用により,GDDR5メモリの抱える問題点は解消できると胸を張る。とくにインパクトが大きいのはメモリチップの実装面積で,仮に容量1GBを実現する場合,GDDR5では2Gbit品が4枚で28×24mmもの広さが必要となるのに対し,HBMならわずかに7×5mmで実現できるという。GDDR5比で約5%(!)という計算である。

|

実際の基板上における総実装面積も,R9 290Xと比較して,ざっくり半分程度の面積で済むとのことだ。これはつまり,従来製品と同程度のグラフィックスメモリ容量を実現する場合,カード長を一気に短くできることを意味する。

|

性能面でも,HBM世代ではGDDR5世代と比べて大幅な向上を期待できると,Macri氏はアピールしている。HBMではGPUとグラフィックスメモリチップが1つのプロセッサ基板上に搭載され,物理的な距離が短くなるため,従来よりも低電圧での駆動が可能になり,消費電力を抑えながら帯域幅を引き上げることができるようになるからだ。

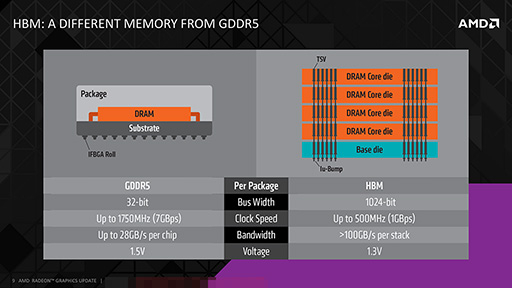

下に示したスライドは,GDDR5メモリ1枚とHBMの積層メモリ1つの仕様を比較したもので,GDDR5メモリだとチップ1枚あたり32bitインタフェースなのが,HBMでは1024bitと一気に拡大する。従来のGDDR5メモリを用いたインタフェースは基板上にバスを配線するため,バス幅の拡大には物理的な限界があるのに対し,GPUパッケージ上に積層メモリを載せるHBMではバス幅を広げることができるのだ。

バス幅が広いため,動作クロックも動作電圧もGDDR5より低いHBMが,3.5倍以上ものメモリバス帯域幅を実現している点に注目してほしい。

|

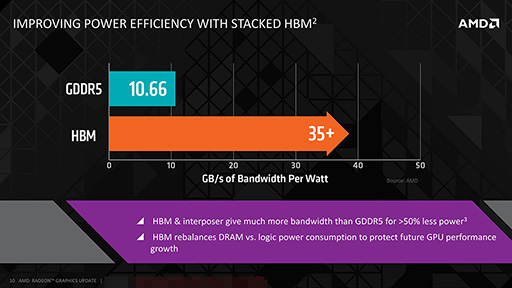

さらに下のスライドは,GDDR5とHBMとで,消費電力1Wあたりのメモリバス帯域幅を比較したものとなる。HBMでは実帯域幅だけでなく,電力効率も3倍以上になるというわけである。

|

ちなみにMacri氏は,次世代GPUのグラフィックスメモリ容量に関して直接的な言及は行わなかった。というか,今回はあくまでもHBMの概要発表であり,次世代GPUに関する言及は何もされなかったのだが,仮に,「積層メモリがメモリチップ4枚で容量1GBを実現し,プロセッサパッケージ上に4つ実装される」という,スライドどおりの構成になるなら,次世代GPUにおけるグラフィックスメモリ容量は4GBということになる。また,その場合,積層メモリあたりの帯域幅が100GB/sだから,総メモリバス帯域幅は400GB/s以上と,512bitメモリインタフェースを持ち,320GB/sのメモリバス帯域幅を持つR9 290Xに対して,そこまで劇的なスペック向上にはならない可能性がある。

最終製品で積層メモリをいくつ搭載してくるか,ここは“GPU戦争”という観点において,重要な注目ポイントとなりそうだ。

GPUだけでなくAPUやモバイル製品へ広がるHBM

将来的には家庭用ゲーム機も視野に

スライドにもちらほらと出てきたとおり,Macri氏は,このHBM技術を,GPUだけでなく,デスクトップならびにノートPC向けのAPUへも広げていくことを明らかにしている。付け加えると,氏は「家庭用ゲーム機にも応用できる技術だ」とも語っていた。電力あたりの性能に優れ,実装面積も小さくて済むHBMは,確かにゲーム機用として最適だろう。

|

気になるのは,Interposerの採用など,実装がやや複雑に見えること。HBM自体の開発コストも含めると,それこそAPUなど,ミドルクラス以下へ展開するには,もう少し時間がかかるのではなかろうか。最初の製品が次世代のハイエンドGPUになるというのは,納得できるところがある。

いずれにせよ,「新世代メモリ技術」と言われていたHBMの世界に,AMDが足を踏み出したことは,大いに注目したいところだ。HBMを採用した次世代GPUの性能がどれほどのものになるのか,期待して待ちたい。

AMD公式Webサイト

- 関連タイトル:

Radeon R9 Fury

Radeon R9 Fury - この記事のURL: