ニュース

AMDのサーバー向け次世代CPU「Naples」は2017年第2四半期に出荷。32コア64スレッド対応でメモリコントローラは8ch,PCIe Gen.3レーン数128

|

登壇したのは,AMDでサーバー部門を統括し,Naples計画を指揮したForrest Norrod(フォーレスト・ノーロッド)氏だ。

|

|

Naplesは32C64Tのサーバー向けCPU

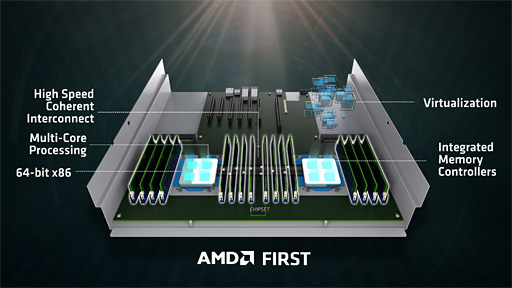

Norrod氏ははじめに,近代CPUやその周辺技術の開発において,AMDが常に先端を切り開いてきたと強調した。具体的な内容は以下のとおりだ。

- 32bitアーキテクチャを採用するx86系CPUとの互換性を維持しながら64bitアーキテクチャへ拡張させた「x64」(AMD64)

- x64系CPUにおける仮想化技術「AMD-V」

- x86系の異種混合マルチプロセッサ計画「Fusion」と,その結実としてのAPU

- CPUとGPUといった異なるプロセッサ間でメモリ空間の一貫性を維持しつつデータを高速にやり取りする仕組み「HSA」(Heterogeneous System Architecture)

- CPU側にメモリコントローラを統合するプロセッサ

|

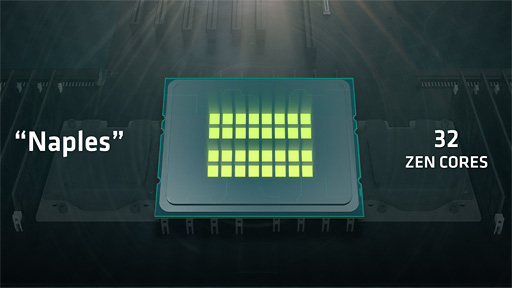

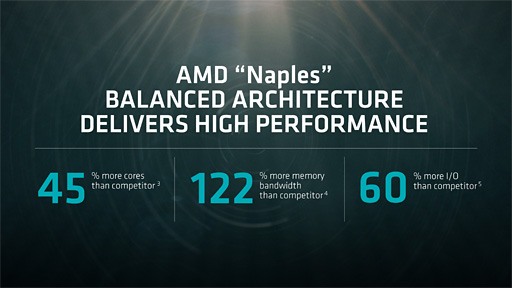

そしてNorrod氏は「今回もまたAMDが最初にやってのけた!」と力強く述べたところで,Naplesが1チップで32基のCPUコアを統合し,SMT(Simultaneous Multi-threading)により64スレッドに対応することをあらためて表明している。これ自体は新情報ではないが(関連記事),「1チップで32コアを統合するx86系CPUはこれが初めて」なのは確かなので,強調したいということなのだろう。

|

今回Norrod氏は,CPUのダイやパッケージの写真は公開しておらず,CPUの実体像は不明だ。Ryzenのように,4コアを「CPU Complex」(CCX)という1モジュールにまとめて,それを8基搭載するデザインなのかどうかも明らかにはなっていない。

|

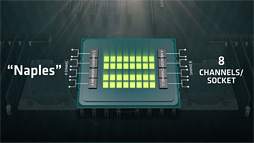

1チップあたりのDDR4メモリインターフェースは8チャンネルの16基DIMMスロットに対応する。最大クロックは2400MHz。最大メモリ容量は1スロットあたりに16GB DIMMを搭載したときの256GBとなる。

|

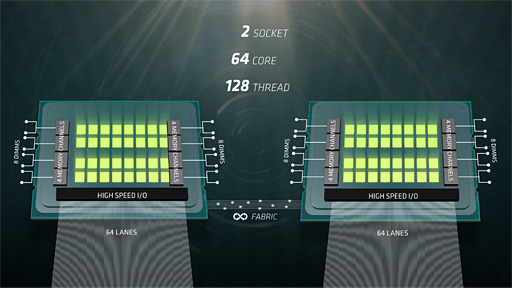

サーバーシステムとしては2ソケット構成まで対応するとのことで,1システムなら64コア128スレッド対応のシステムを構築できることになる。2-way構成の場合,PCI Express Gen.3のレーン数は1ソケットあたり64,2ソケットの合計で128という仕様になるそうだ。最大メモリ容量は単純に2倍の512GBとなる。

なお,2つのソケットの互いのCPU間のデータのやりとりには,Ryzenで初採用となった「Infinity Fabric」を採用している。

|

|

Radeon Instinct搭載のGPUサーバー用としても期待されるNaples

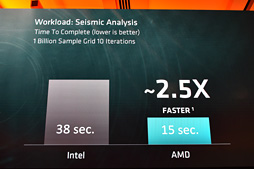

「実際にどのくらい性能があるのか」についてAMDは,超多次元配列で持たせた3Dベクトルデータに対する演算を10回行わせるベンチマークを実際に実行し,完了までの速度比較を競合製品と行うことで誇示した。

このような,「ベクトルデータの配列構造」を対象にする多次元グリッド計算は,地震学や気象学などの自然科学技術シミュレーション,医療技術や新薬開発のシミュレーション,建築学や機械工学,熱力学における構造解析では定番の計算モデルである。

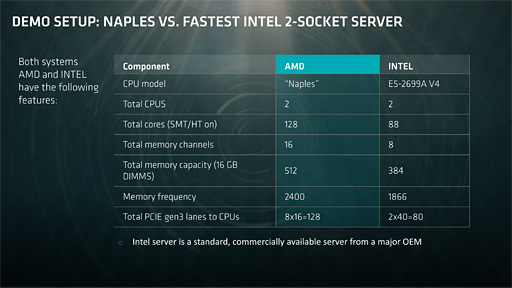

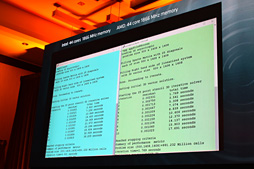

さて,最初のテストは,「500×1408×1408の3次元配列で管理される約10億個のベクトルデータを読み出して計算する」というものを,NaplesとXeon E5-2699A V4で比較するものだ。ここでは44コア88スレッド,DDR4-1866と条件を揃えたが,結果は,Naplesが比較対象に対して約半分の時間で計算を終えていた。

|

|

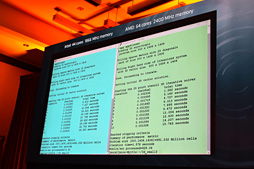

続くテストは,データセットは変えず,Naplesはスペックに遠慮なしの64コア128レスレッド,DDR4-2400アクセスするというのものだ。こうなるとNaplesは,Xeon E5-2699A V4に対して2.5倍の速度性能を示す。

|

|

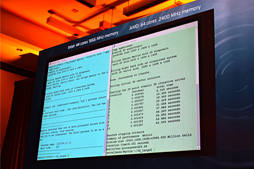

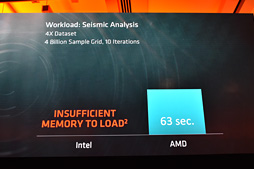

最後は,直前のテスト条件から,取り扱うデータサイズだけ,2000×1408×1408の3次元配列で管理される約40億個のベクトルデータとしたものになるが,Xeon E5-2699A V4では,メモリ不足エラーが出て実行不能という結果に。これは「Naplesのほうがより大きいデータセットを扱える」ことのアピールというわけである。

ちなみにNaples側の計算時間は,データ規模の拡大倍率分長くなるだけで済んでいた。

|

|

地味な画面のテストではあったが,大規模データに対する計算速度,扱えるデータ量の限界値の高さという,現在のサーバーに求められる性能において,XeonよりNaplesのほうが優れているというアピールだったわけだ。

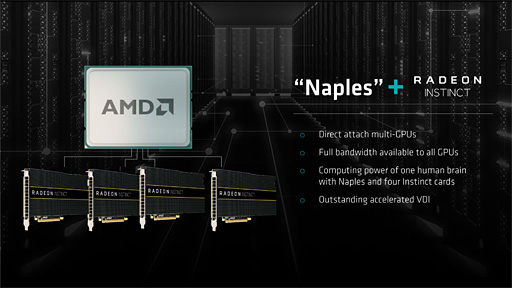

さて,最後にNorrod氏は,発表済みのGPGPU専用GPUカード「Radeon Instinct」とNaplesの相性が抜群であると述べている。

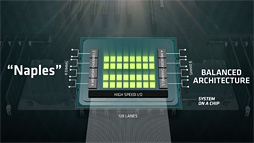

グラフィックス描画においては,描画コマンドを解釈してからGPU側で処理が“爆発”するので,CPUとGPU間のバス消費はPCI Express Gen.3の8レーン程度でも問題ないというのがAMDの見解だ(関連記事)。

しかしGPGPU用途では,処理する対象データそのものをCPUとGPUとでやりとりする頻度が上がるため,GPUとはPCI Express Gen.3の16レーンで接続したほうがよい。

その点Naplesのシステムならば,PCI Express Gen.3は128レーンも出ているので,仮に4基のRadeon Instinctを16レーン

|

デスクトップPC市場でRyzen 7がちょっとしたセンセーションを巻き起こしたばかりのタイミングだが,今後AMDは,サーバー市場にも大きな波風を立てるかもしれない。今から要注目だ。

|

AMD公式Webサイト

※11:20頃追記

AMDから販売計画に関する情報のアップデートが入ったため,記事をアップデートしました。

- 関連タイトル:

Ryzen(Zen,Zen+)

Ryzen(Zen,Zen+) - 関連タイトル:

EPYC

EPYC - この記事のURL: