ニュース

「Project Denver」とTegraは無関係!? HPC・GPU・モバイル向けで“3極化”するNVIDIAのCPU戦略

もともとProject Denverは,今から約3年半前に,GPUの並列演算処理性能を向上させるために,GPU内部のスケジューリングや命令発行を制御する,より強力なプロセッサが必要だとして始まったとされる。

だが,「Windows 8」という開発コードネームで呼ばれる次期Windows(以下,Windows 8)のARMアーキテクチャ対応によって,状況は大きく変わってきた。今回はNVIDIAのGPUコンピューティングへ向けた取り組みと,今後のCPU開発について整理してみよう。

限界にさしかかったCPUの性能向上

|

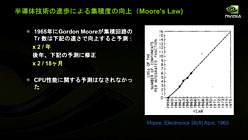

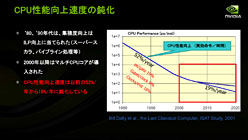

そこでまず馬路氏が述べたのは,18か月で2倍のトランジスタ集積度を実現するという「ムーアの法則」の恩恵を受け,CPUが順調に性能を伸ばしてきたのは2000年までだった,という話だ。

氏によると,2000年までの間,

- プロセス技術の進化に伴うトランジスタ速度向上:19%

- パイプラインーF/F(フリップ・フロップ,入力信号“0”または“1”を一時的に保持する論理回路)間の論理ゲート数削減:9%

- マイクロアーキテクチャの改良:18%

によって,実行性能は,

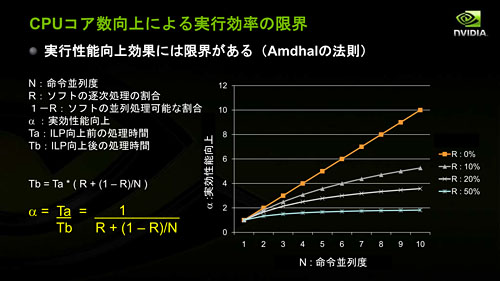

と,毎年52%の性能向上を果たしてきたのこと。しかし2000年以降,とくにCPUのマルチコア化が加速された2005年以降は,複数のプロセッサによる並列コンピューティング性能の向上度合いに関する法則として注目されている「アムダールの法則」(Amdahl's Law,Gene Amdahl氏が提唱したことからそう呼ばれる)が壁として立ちはだかっているという。

|

|

|

アムダールの法則では,「演算処理の並列度を高めるためにCPUのコア数を増やしても,アプリケーションで並列処理できない部分があった場合,その比率(≒ソフトの逐次処理の割合)の大きさによっては,マルチコア化に比例した実効性能の向上は望めない」とされる。馬路氏は,マルチコアCPUに最適化されていないアプリケーションだと,逐次処理の割合が20〜50%に達するとし,「8コアCPUをもってしても,実効性能向上幅はシングルコア比の4倍に満たないのが現状で,2000年以降,CPUの性能向上速度は年19%にまで鈍化している」と指摘する。

|

|

|

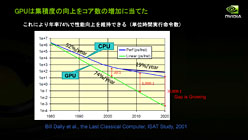

ただ,それにも限界はあり,結果として,スーパーコンピューティングの世界では,並列演算性能を追求したアーキテクチャになっているGPUコンピューティングが注目されている。

|

GPUコンピューティングの現状

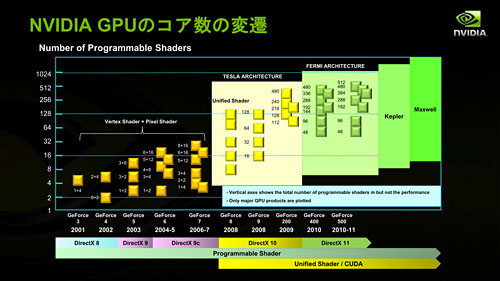

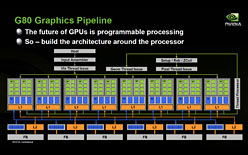

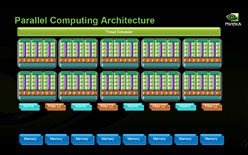

半導体プロセス技術の進化とともに,コア数を大きく増やしてきたGPUは,統合形シェーダアーキテクチャへ移行したDirectX 10以降,並列演算処理性能を高めるべく,CPUよりも早いペースでアーキテクチャの改良を繰り返し,汎用コンピューティング性能も高めてきた。

|

|

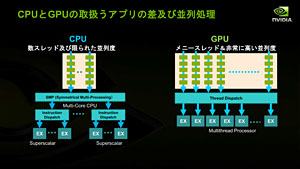

| CPUとGPUそれぞれの並列処理イメージ |

|

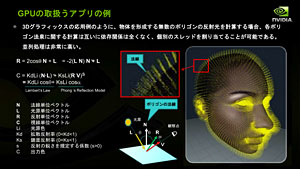

| GPUでは,各ポリゴンに関する法線処理には互いに依存関係がないため,それぞれに個別のスレッドを割り当てれば,複雑なキャラクター描画などを効率よく実現できる |

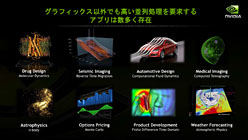

こういった並列処理性能は,科学演算処理などの高速化を可能にすることから,NVIDIAはGT100コアを採用する初代「Tesla」以降,より汎用的な大規模超並列処理ができるよう最適化を図ってきたと,馬路氏は述べている。

|

|

独自CPUコア開発は必然の産物

といっても,GPUとてアムダールの法則とは無縁ではない。今後もGPUコアが増え続ければ,当然のことながら壁に突き当たることとなる。

とくにボトルネックが生じやすいのは,増え続けるGPUコアを効率よく制御するためのスケジューリングや命令発行を司るコントローラ機能周りだ。

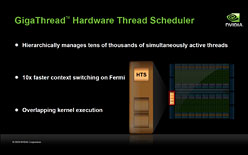

|

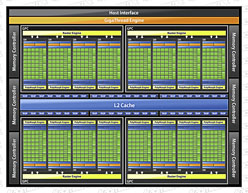

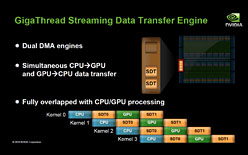

その後,メニーコア化が進むなか,Fermiアーキテクチャでは,Thread Schedulerを「GigaThread Engine」へと大幅に強化。それまでは逐次実行しかできなかったカーネルプログラム(GPUを制御するためのプログラム)の同時実行に対応し,より並列処理性能を高める取り組みも行われている。

|

|

|

|

|

同社でプロダクトマーケティングを担当副社長を務めるUjesh Desai(ユージェッシュ・デサイ)氏も「Project Denverは,GPUへの統合をターゲットとして,3年前に開発がスタートした」と認めている。

|

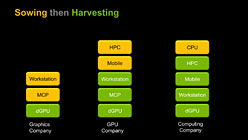

NVIDIAの目指す「Computing Company」では,CPUも重要な収益源となる |

2011年5月に示された,Project Denverプロセッサコアのイメージ |

|

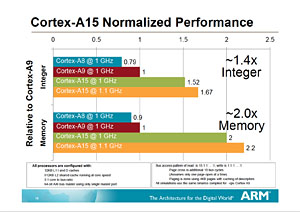

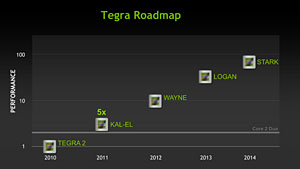

NVIDIAでTegraビジネスを統括するMichael Rayfield(マイケル・レイフィールド)氏いわく,「Project DenverとTegraは無関係だ」。氏は,「省電力性が最重視されるTegraで冒険はしにくいため,当面はARMのロードマップに沿ったSoC開発を進めていく」とし,「Kal-ElはCortex-A9のクアッドコア,Wayneでは“その次のアーキテクチャコア”を採用するのが自然な流れだ」と述べている。つまりWayneでは,Cortex-A15コアを採用するということだ。

Desai氏も,「Project Denverは,HPC向けプラットフォーム向けとなる高性能CPUコアをターゲットとしており,Tegraに収まる消費電力ではない」と述べ,Rayfield氏の発言を裏付けている。

Project Denverの目的とは

|

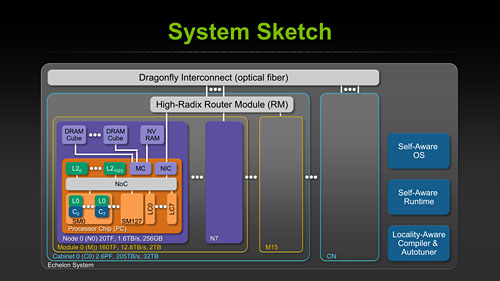

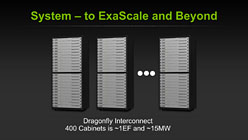

Echelonというのは,米国防総省の先端技術開発研究を担うDARPA(Defense Advanced Research Project Agency,国防高等研究計画局)主導の下,2018年にエクサスケールスーパーコンピュータを実現する「Ubiquitous High Performance Computing」(以下,UHPC)向けプロジェクトのこと。NVIDIAはEchelonに向けた研究助成金を受けているため,その「Phase1」期限となる2014年までにハードウェア設計を完了し,DARPAの審査を受ける必要があるのだ。

|

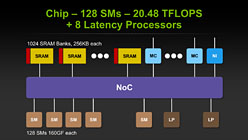

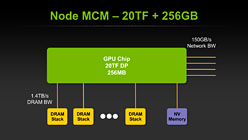

各SMは「NoC」(Network on Chip)と呼ばれる内部インタフェース経由でL2キャッシュやメモリコントローラ,別のSMなどと相互接続される。L2キャッシュはCUDA Core数と同じ1024個のバンクを備え,チップパッケージ上で接続されるDRAM「DRAM Cube」と1.4TB/sの広帯域幅で結ばれるのも特徴だ。

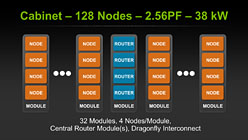

Echelonチップのピーク演算性能は倍精度で20TFLOPSに達し,「Echelonチップ4基をまとめたモジュール」を32基搭載したキャビネットで2.56PFLOPS(ペタフロップス)を実現する見込み。NVIDIAは,この基本設計を基に,Phase2では演算性能と省電力性を向上させる考えを持っている。

|

Echelonでは,128個のSMと8つのLatency Processorを統合。Latency ProcessorはDenverコアのこと |

メモリもMCM(Multi Chip Module)で同一パッケージ上で接続し,DRAMスタックとは1.4TB/sの帯域を実現 |

|

|

|

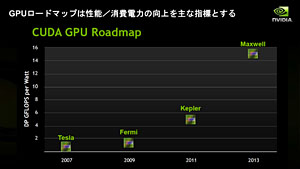

| NVIDIAのGPUロードマップ |

|

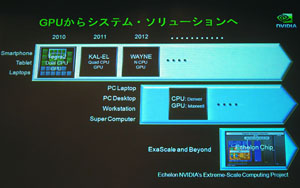

| GTC Workshop Japan 2011で公開されたプラットフォームロードマップ |

そしてこのことは,GTC Workshop Japan 2011で公開されたプラットフォームロードマップとも符合する。同イベントでは,Project Denverが,2013年登場予定の次次世代GPU「Maxwell」(マクスウェル,開発コードネーム)と同じタイミングで投入されることが示唆されているのだ。示されたスライドでは,DenverとMaxwellが同じ枠内に収まっていたが,Echelonと同様,MaxwellにもDenverコアが統合される可能性があると見ていいのではなかろうか。

もっとも,GPGPU用途だけではなく,3Dアプリケーション向けのGeForceとしても利用されるMaxwellでは,汎用コンピューティング専用チップとなるEchelonほどアグレッシブなアーキテクチャが採用されるとは考えにくい。

先ほどEchelonは1024コアで20TFLOPSを実現すると紹介したが,MaxwellがFermi世代と同じ消費電力の枠内,TDP(Thermal Design Power,熱設計消費電力)でいうと250W以下のレベルに収まるなら,倍精度演算性能は3.5〜4TFLOPS(Teslaの15倍,Fermiの7.5倍)あたりになるだろう。

EchelonとMaxwellでは,GPU性能そのものにも大きな違いが生じることになるはずだ。

|

Desai氏は,「『CPUコアの開発』は,すでに複数のプロジェクトが進行している」と,筆者に語っている。そして業界関係者も,Project Denverにはさらにもう1つのオプション――Windows 8ベースのノートPC向けSoC(System-on-a-Chip)――があると見ている。

念のため繰り返しておくと,EchelonやMaxwellがターゲットで,消費電力も大きなDenverコアが,そのままノートPC向けSoC製品として市場投入される可能性は低い。また,TegraにDenverコアを統合する計画は(少なくとも当面の間は)なく,付け加えるなら,2011年2月の「Mobile World Congress 2011」で公開されたロードマップは,あくまでもスマートフォンやタブレット向けのものだ。

ただ,2013年にはIntelやAMDも薄型ノートPC向けCPUをSoC化する計画があるなか,せっかくARMアーキテクチャがサポートされたにもかかわらず,NVIDIAが“Windows 8世代のノートPC市場”へ参入しない理由もない。

|

Stark以降,Project Denverを活かしつつ,NVIDIAがTegraプラットフォームをどのように拡張していくのか,注目していきたい。

いずれにせよProject Denverは,NVIDIAにとって,来るべきヘテロジニアスコンピューティング時代におけるイニシアティブを握るうえで極めて重要な計画だといえる。GPUコンピューティング向けプロセッサ,3Dゲーム用GPU,そしてTegraといった同社の主要製品群に,大きな変革をもたらしそうだ。

- 関連タイトル:

Project Denver(開発コードネーム)

Project Denver(開発コードネーム) - 関連タイトル:

Tegra

Tegra - 関連タイトル:

GeForce GTX 900

GeForce GTX 900 - この記事のURL: