ニュース

2009年旧正月明け特別企画(2):AMDのCPU&チップセットロードマップを整理する

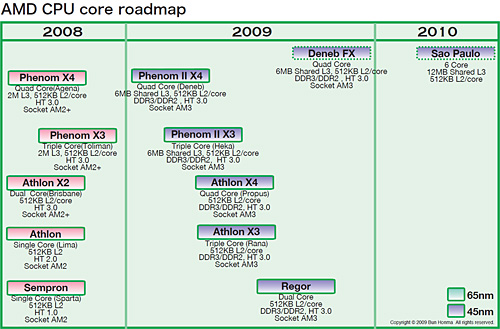

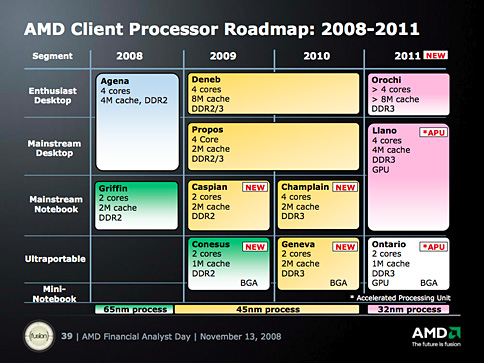

台湾や中国のPCベンダーやPCパーツベンダーが動き出したこのタイミングで,2009年のPC業界を占う特別企画の第2弾。初回にIntelのデスクトップPC向けCPU&チップセットのロードマップを確認したが,今回は,1月に「Deneb」こと「Phenom II」を投入したAMDのデスクトップPCおよびノートPC向けプラットフォームのロードマップをチェックしてみたい。

→2009年旧正月明け特別企画(1):IntelのデスクトップPC向けCPU&チップセットロードマップを整理する

→2009年旧正月明け特別企画(3):グラフィックス&DirectXロードマップを整理する

|

日本時間2009年2月8日に,AM3パッケージのPhenom II X4/X3を発表した(関連記事1,関連記事2)同社は,2月中にこれらを市場投入する予定。主要マザーボードベンダーのSocket AM3搭載製品も,第1四半期中には市場に出揃う見込みだ。ただし,ハイエンドモデルのAM3版が登場するのは,第2四半期以降になる見通しとなる。

「AMDは2008年末ギリギリのタイミングまで,Phenom IIをAM3パッケージで一本化する道を探っていた」と,大手OEM(Original Equipment Manufacturer,ここでは「相手先のブランドでPCを製造する企業」のこと)関係者は証言する。「しかし,DDR3メモリモジュールの動作検証やパフォーマンスチューニングの遅れから,Socket AM2パッケージを採用した『Phenom II X4 940 Black Edition/3.0GHz』と『Phenom II X4 920/2.8GHz』を先行投入せざるを得なかった」という。

そんなAMDのAM3パッケージ第1弾製品は最終的に,(日本国内で店頭販売されないモデルも含め)下記のとおりのラインナップになるようだ。800番台のモデルナンバーを持つPhenom II X4は,L3キャッシュ容量が同900番台の6MBから4MBへと削られた下位モデルで,また,同700番台のPhenom II X3は,開発コードネーム「Heka」(ヘカ)の名で知られてきた,トリプルコアCPUとなる。

- Phenom II X4 925/2.8GHz

(L2キャッシュ容量512KB×4,L3キャッシュ容量6MB,TDP 95W) - Phenom II X4 910/2.6GHz

(L2キャッシュ容量512KB×4,L3キャッシュ容量6MB,TDP 95W) - Phenom II X4 810/2.6GHz

(L2キャッシュ容量512KB×4,L3キャッシュ容量4MB,TDP 95W) - Phenom II X4 805/2.5GHz

(L2キャッシュ容量512KB×4,L3キャッシュ容量4MB,TDP 95W) - Phenom II X3 720 Black Edition/2.8GHz

(L2キャッシュ容量512KB×3,L3キャッシュ容量6MB,TDP 95W) - Phenom II X3 710/2.6GHz

(L2キャッシュ容量512KB×3,L3キャッシュ容量6MB,TDP 95W)

ここで重要なのは,先行投入されたPhenom II X4 940 Black Edition(以下,Phenom II X4 940)と同じ,もしくはそれを上回る動作クロックの製品が存在しないことだ。先ほどの関係者によると,AMDがPhenom II X4 940の上位モデルをAM3パッケージで投入するのは,2009年第2四半期半ば以降になる見込みだという。

|

もっとも,PhenomファミリーのCPUは,メモリコントローラをCPUに内蔵し,L3キャッシュでメモリアクセスのレイテンシを隠蔽してきた実績がある。DDR3移行に伴うバス帯域幅の向上が,Intelのプラットフォーム移行(※Core 2→Core i7)ほどのインパクトを持たないのは,やむを得ないところである。

また,メモリの互換性については,「Core i7の登場で,1.5V〜1.65動作のDDR3モジュールが出揃ってきたことを考えれば,メモリ互換性の問題はさほど深刻な問題とはならないだろう」と見る関係者も多い。

AM2+時代と同様,CPUコアとメモリコントローラなどの非コア部で独立した電源系統を持つAM3版CPUでは,Core i7よりも柔軟な電圧設定が可能だ。その意味で,AMDがAM3パッケージ投入の第1段階でハイエンド製品を市場投入しないのは,「Phenom II X4の上位モデルを,Core i7の上位モデルと十分戦えるレベルまでチューニングするための時間稼ぎ」と見ることも可能だろう。

AM3版のフラグシップ製品が投入される頃には,DDR3プラットフォームであることを最大限に生かした,より高いパフォーマンスを発揮するものになっているのを期待したいところだ。

メインストリームCPUもクアッドコア化

AMDは2009年第2四半期に,同社がMainstream(メインストリーム)と位置づける,エントリークラスPC向けデスクトップCPUのラインナップ強化も図る。

同社はこのクラスのCPUに,継続して「Athlon」ブランドを採用する計画で,クアッドコアの「Propus」(プロパス,開発コードネーム)が「Athlon X4」,トリプルコアの「Rana」(ラナ,同)が「Athlon X3」となる予定だ。また,現行のAthlon X2も,2009年第3四半期には45nm SOIプロセス世代へ移行した「Regor」(リゴル,同)コアを採用することになる。

|

これらはいずれもAM3パッケージを採用し,デュアルチャネルDDR3-1333をサポート。Athlon X4/X3は,Phenom II X4/X3からL3キャッシュを省略した形を採るが,これがPhenom X4 9000番台(開発コードネーム「Agena」)とAthlon X2 7000番台(開発コードネーム「Kuma」)の関係のように,同じシリコンを共用するのか,L3キャッシュを省いた別シリコンとしてデザインされているのかは,現時点では明らかにされていない。

Phenom II X4では,L3キャッシュがシリコンの大きな部分を占めているだけに,もし,後者の手法が採用されるのではあれば,大幅なコストダウンと大量生産が可能になるはずだ。

なお,Athlon X4/X3には,低消費電力版も用意される予定。OEM関係者によれば,そのTDP(Thermal Design Power,熱設計消費電力)は65Wとなっているが,AMDは「TDP=最大消費電力」としているので,相対的にIntelの65nmプロセス版Core 2 Quadよりは低消費電力で動作することになるだろう。

2009年第2四半期に市場投入が予定される,Athlon X4/X3のラインナップは下記のとおりである。

- Athlon X4 615/2.7GHz

(L2キャッシュ容量512KB×4,TDP 95W) - Athlon X4 605/2.5GHz

(L2キャッシュ容量512KB×4,TDP 95W) - Athlon X4 605e/2.5GHz

(L2キャッシュ容量512KB×4,TDP 65W) - Athlon X3 420/2.8GHz

(L2キャッシュ容量512KB×3,TDP 95W) - Athlon X3 410/2.6GHz

(L2キャッシュ容量512KB×3,TDP 95W) - Athlon X3 405e/2.5GHz

(L2キャッシュ容量512KB×3,TDP 65W)

モバイルCPUはアーキテクチャ変更でコア性能向上へ

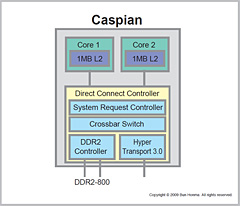

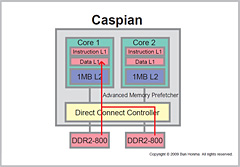

モバイルCPUでは,開発コードネーム「Caspian」(カスピアン)と呼ばれる新コアが,2009年後半に市場投入される。

|

Caspianの各コアに内蔵されるFPUは128bit精度で,1基のCPUが四つの倍精度浮動小数点演算を1サイクルでこなせるようになる。

また,従来のK8アーキテクチャでは,128bit SSE命令は二つに分けて実行する必要があった。これに対してCaspianのFPUは128bit幅のSSE処理を担当可能で,しかも,同時に二つの処理をこなすことができる。つまり,Caspianでは,ゲーム物理の演算やビデオデータのトランスコードなど,SSEが“効く”処理の性能が大幅に向上することを期待できるというわけである。

|

AMDが,CaspianでモバイルCPUのアーキテクチャに大きく手を入れたのは,同アーキテクチャがグラフィックスコアと統合を果たす,“Fusion”とのベースとなるCPUコアだからだ。

AMDは2011年に,開発コードネーム「Liano」(リャノ)として知られるAPU(Accelerated Processing Unit)を市場投入する意向を表明しているが,そのCPUアーキテクチャが,このCaspianと同じものになる見通しである。Lianoは,四つのCPUコアとGPUとを32nmプロセスで統合し,ノートPC向けのみならず,メインストリームデスクトップPC市場へも投入される。

|

32nmプロセス世代というと,2011年にはデスクトップPC向けCPU「Orochi」(オロチ,開発コードネーム)も計画されている。2008年末に開催された「AMD 2008 Analyst Day」で,Orochiは4コア以上,合計8MB以上のキャッシュを搭載するとしか公表されていないが,大手OEM関係者によると,「コアデザインはサーバー向けCPUと共用するため,8コア仕様になる可能性が高い」とのことだ。

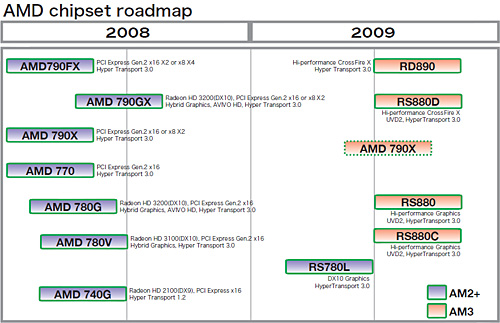

新チップセットRD890/RS880Dが下半期にデビュー

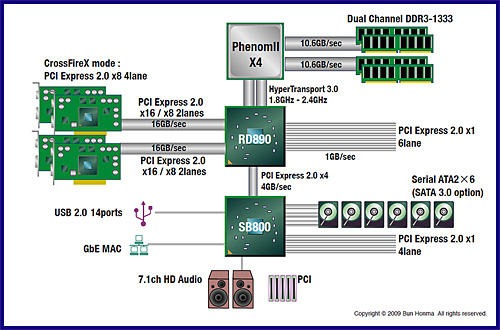

AM3パッケージのCPUは,現行の「AMD 790FX/GX」チップセットと組み合わせられるが,2009年後半には,これらの機能強化版となる開発コードネーム「RD890」「RS880D」が投入される見通しだ。

|

単体(discrete)チップセットとなるRD890は,“AMD 790FXの強化版”という位置付けで,ATI CrossFireXパフォーマンスの向上と,AM3版CPUへの最適化,AMD OverDrive 3.0のサポートなどが行われる見込み。マザーボードベンダー関係者によると,AMD 790FXと比べたときに,革新は限定的なものに留まるという。

一方のRS880Dは,“グラフィックス機能統合型RD890”とでも言うべき製品になる。グラフィックスコアの動作クロックが引き上げられるとともに,ATI Raden HD 4000シリーズに搭載されている第2世代のUVD(Unified Video Decoder)が搭載されることで,動画再生支援機能が強化される予定だ。

これに伴い,その下位モデルとして,「AMD 780G」後継となる「RS880」(開発コードネーム)も用意される予定となっている。

これら新世代チップセットでは,サウスブリッジとして,Serial ATA 3.0をサポートした「SB800」が組み合わせられる見込みだ。

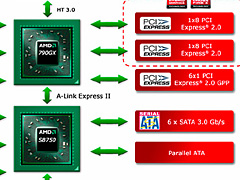

AMD 7シリーズのチップセットは,サウスブリッジとの接続に「A-Link Express II」と呼ばれるPCI Express x4インタフェースを採用しているが,SB800シリーズではこれが,「A-Link Express III」と呼ばれるPCI Express 2.0 x4インタフェースへと変更される。これは,AMDのチップセットにとって,非常に大きな革新だ。

|

これに対してSB800では,ノースブリッジとの帯域幅が単純計算で倍に拡大するため,SB800側に1000BASE-T LANコントローラの論理層(GbE MAC)が内蔵される予定。さらに,同じ理由でAMD 7ではノースブリッジ側に用意されていたPCI Express 2.0 x1のサポートも,SB800側でも可能になる。

AMDはもともと,このSB800を,2009年に市場投入する計画だった“幻のFusionプロセッサ”,「Swift」(スイフト,開発コードネーム)向けに開発していたと言われている。大手OEM関係者によれば,GPUをCPUに統合するSwiftで,ノースブリッジを省いてサウスブリッジと直接つなげる2チップ構成を実現すべく開発されてきたのが,SB800だというのだ。

このコンセプトが,2011年にズレ込んだFusion APUでも継承されるのかどうかは分からないが,ノース&サウスブリッジ間の帯域幅が広がれば,I/Oスループットの向上が見込めるので,いずれにせよ歓迎すべき進化といえる。

AMDは,SB800におけるSerial ATA 3.0対応をオプションとしつつ,2009年第4四半期までにSB800を投入したい考えのようだ。言い換えると,RD890/RS880Dチップセットの登場当初,サウスブリッジには現行のSB750が組み合わせられることになる。

- 関連タイトル:

Phenom II

Phenom II

- 関連タイトル:

AMD 8

AMD 8 - 関連タイトル:

Caspian(開発コードネーム)

Caspian(開発コードネーム) - この記事のURL: