イベント

西川善司の3DGE:Zen 2×PCIe4時代のAM4プラットフォームアップグレード指南〜PCIe4の直接の恩恵はグラフィックスよりもストレージのパフォーマンス?

|

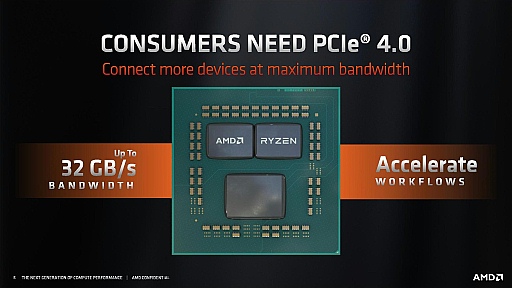

AMDのRyzen 7 3000シリーズは,競合に先駆けて,PCI-Express Gen.4に対応する業界初のCPUであり,Radeon RX 5000シリーズも同様に民生向けとしては業界初のPCI-Express Gen.4に対応GPUになる。

ただ,Ryzen 7 3000シリーズの対応ソケットは先代Ryzenまでと同様のAM4であり,実際,AMDはRyzen 7 3000シリーズを既存のマザーボードに搭載することができることを訴求している。だったら,既存AM4マザーボードにRyzen 7 3000シリーズを差したらPCI-Express Gen.4が使えるようになるのだろうか。

|

第3世代Ryzen 3000シリーズはどこまで昔のAM4プラットフォームに対応できるの?

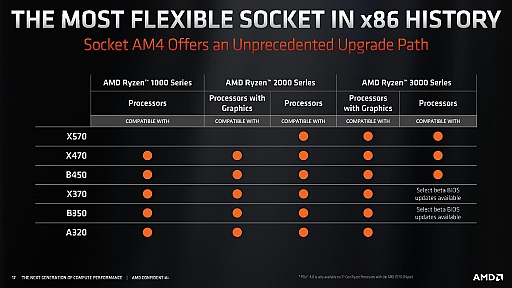

まず,一番気になる互換性について,AMDは下のような表を示している。

|

まず,最新の第3世代Ryzen 3000シリーズは,この新Ryzenとともに登場する最新チップセットのX570に適合するのは当然として,第2世代Ryzen 2000シリーズとともにリリースされたX470/B450の400型番チップセットに対応する。

第1世代Ryzen 1000シリーズとともにリリースされたX370/B350/A320の300型番チップセットについてはちょっと注意が必要となる。

まず,名前としてはRyzen 3000シリーズであっても,中身としては「ZEN+」ベースであるAPU版(Processors With Graphics)のRyzen 3000シリーズについては,X370/B350/A320のすべての300型番チップセットに対応できるが,「真の」ともいうべき「Zen 2」ベースのRyzen 3000シリーズについては,「マザーボードメーカーが対応BIOSをリリースした場合に限って」という断り書きが付いたうえでX370とB350のチップセットにも対応する。「ではA320はどうなんだ?」という話になるのだが,「Hallock氏は技術的には対応可能だが,その判断はマザーボードベンダーに委ねられている」という言い方をしていた。

300型番のチップセットは,APUのソケットがそれまでのFM2系ソケットからAM4ソケットに変わった頃に登場したものだ。この当時のAPUの開発コードネームは「Bristol Ridge」で,とくにA320チップセットは最もエントリークラスに向けたマザーボードに採用されていた。おそらくAMDとしてもマザーボードメーカーとしても「A320は切り捨てても実害はない」という判断を行ったのだと思われる。

逆に最新のX570チップセットは,Zen+コアベースの第2世代Ryzen 2000シリーズにまでは適合できるが,初代ZenコアベースのRyzen 1000シリーズや,2000型番は付いているが中身が初代ZenコアベースのAPUには適合しない。

総じて,ややこしくしているのは,APU版Ryzenが「型番のサバ読み」をしているところにあったりする。注意したいポイントだ。

PCI-Express Gen.4はX570チップセットと組み合わせたときだけサポートされる〜例外もあり?

続いては,PCI-Express Gen.4絡みについてだ。

PCI-Expressインタフェース自体はRyzen CPU側に実装されているのだが,結論から言うと,最新のX570チップセット以外との組み合わせではPCI-Express Gen.4は有効にならない。

前述したように300型番/400型番でも第3世代Ryzen 3000シリーズは使えるが,基本的にはPCI-Expree Gen.4対応にならない。ベーシックな理解としては「PCI-Exress Gen.4の利用にはX570チップセットが必要」ということになる。

|

ただし,ここにも例外がある。

すでに海外のニュースサイトでも報じられているように「第3世代Ryzen 3000シリーズを挿したときに限り,400型番のチップセットマザーボードでもPCI-Express Gen.4が有効になる場合がある」という事例があるのだ。

以前,この記事でも触れたことがあったが,PCI-Express Gen.4のインタフェース自体はCPU側から提供されており,コントローラハブからエンドポイントデバイスまでの回路などは400型番以前のチップセットも500型番のチップセットも共通なので,マザーボードメーカーが既存の400シリーズチップセット搭載マザーボードで(PCI-SIGの)PCIe Gen.4認証試験を通せば,当該マザーボードをGen.4で運用することはできる。実際,そうしたマザーボードも出てきているようなのだ。

まぁAMDとしては例外事項については対応しきれないので表向きとしては「PCI-Exress Gen.4の利用にはX570チップセットが必要」といいきっているわけである。

なお,改めて言うまでもないかもしれないが,中身がZEN+ベースのAPU版のRyzen 3000シリーズは,X570チップセットと組み合わせてもPCI-Express Gen.4サポートにはならない。Gen.3までの対応となる。

|

40レーン分のPCI-Express Gen.4環境を提供するX570チップセット時代のAM4プラットフォーム

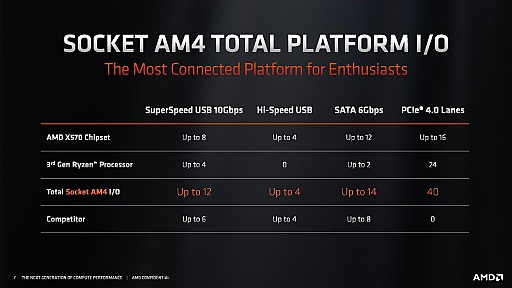

Hallock氏は,続いて,第3世代Ryzen 3000シリーズとX570チップセットが提供するPCI-Express Gen.4プラットフォームの優位性について解説してくれた。

下図は第3世代Ryzen 3000シリーズとX570チップセットが提供するPCI-Express Gen.4のレーン数とそのほかのI/Oポートの個数などをまとめた表になる。

|

第3世代Ryzen 3000シリーズ自体はPCI-Express Gen.4を24レーン提供する。このうち4レーンはチップセットとCPU間のリンクに用いられる。Gen.4とGen.3の違いはあるがこの割り当て構成自体は第2世代Ryzen 2000シリーズと同じである。

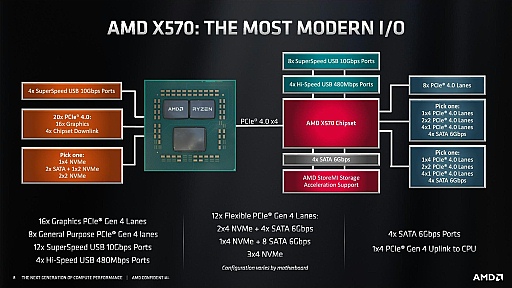

下図は第3世代Ryzen 3000シリーズとX570チップセットの組み合わせで提供するI/O構成を図解したものだ。こちらもGen.4とGen.3の違いはあるがこの割り当て構成自体は第2世代Ryzen 2000シリーズと400型番チップセットのときと変わらない。

|

X570チップセット自体はPCI-Express Gen.4を16レーン提供するが,その割り当て構成はマザーボードベンダーの設計思想に委ねられる。そのバリエーションについては上の図の右側の「Pick One」(このうちのどれか一つ)の所に示されている。

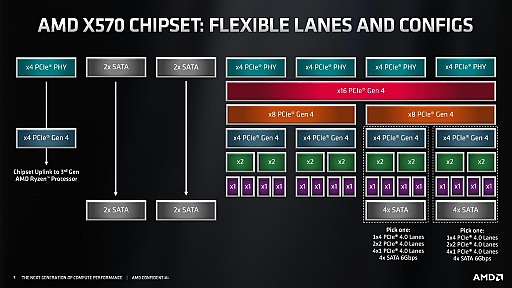

この組み合わせバリエーションをより分かりやすく図解したのが下図だ。

|

16レーンをそのまま丸ごと提供する製品は希で,実際には8レーンをセカンダリGPU用途に割り当てるなどして,残り8レーンを汎用I/Oなどに割り当てる構成が一般的だ。

Ryzenの場合,USBなどの汎用I/Oによって入出力されるデータ群も,最終的にCPU-チップセット間を往来する際にはPCI-Expressを利用して行われる。その根幹伝送ラインがPCI-Express Gen.4では従来のGen.3の2倍となっているのだから,汎用I/Oポートも多く提供できる……というのが副次的なPCI-Express Gen.4のメリットとしてAMDはアピールしていた。

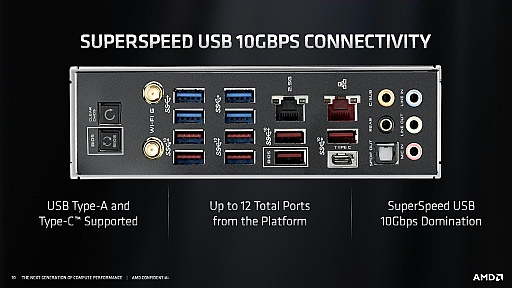

下図は,とあるX570マザーボードのバックパネルだが,USB 3.1 Gen.2のSuperSpeedPlus USB 10Gbpsのポートを4ポートも提供できている。Hallock氏は「こんなマザーボードはいまのところAMDのX570プラットフォームだけ」と強調していた。

|

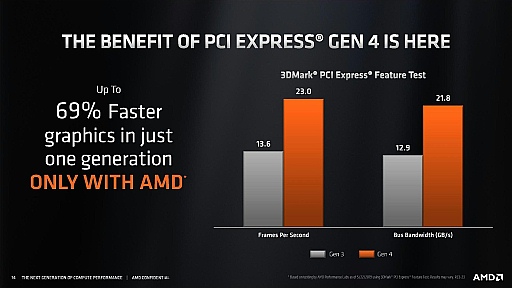

PCI-Express Gen.4の直接的な恩恵はグラフィックスではない。むしろストレージスピードの向上にあり

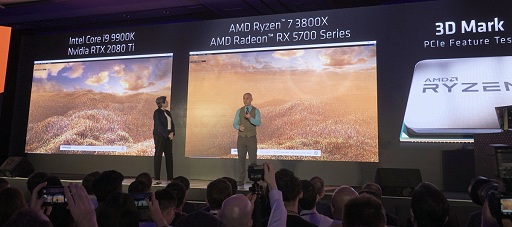

AMDのCOMPUTEX 2019基調講演では,PCI-Express Gen.4の優位性について,グラフィックスベンチマークで見せていたが,Hallock氏は,「あれは一目見て違いを分かりやすく伝えるためのもので,多くのゲームグラフィックスにおいては,PCI-Express Gen.4の優位性は感じられないかもしれない」と述べる。

|

そう,実はゲームグラフィックスを司るグラフィックスエンジンは,レンダリング前に必要なデータのほとんどを先にグラフィックスメモリに送ってしまい,実際の描画が始まった際には,むしろ描画コマンドとその付随データの伝送以外には極力PCI-Expressバスを使わないように設計しているのだ。

基調講演で見せられたあのPCI-Expressテストは,いわば「テストのためのテスト」といった風情のものだったわけだ。

|

|

では,PCI-Express Gen.4の当面の直接的な恩恵はどこにあるのか。「それはストレージスピードだ」とHallock氏はいう。

現在のNVMe SSDの読み書き(アクセス)の際に生じるデータ伝送はPCI-Expressが利用されているので,ここが従来のGen.3に対して2倍に高速化されるGen.4であれば,実効アクセス速度の向上が見込めるわけである。

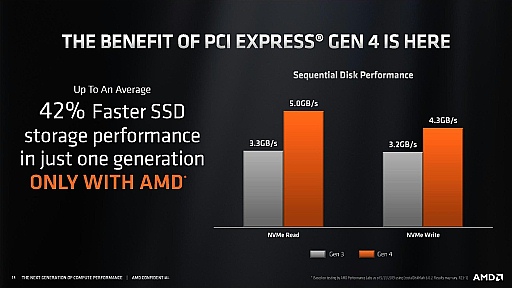

下にAMD調べのNVMe SSDのシーケンシャルリード/ライトのパフォーマンス測定結果を示しておくが,同一NVMe SSDを用いたテストでも,PCI-Express Gen.3システムからGen.4に置き換えただけで,なんと42%ものパフォーマンスアップが実現されたというから興味深い。

|

Hallock氏は「ストレージへのアクセスはPCオペレーションの中でももっともプレイヤーのPC使用時の体感速度を決める要素であり,SSD環境が主流になってきている昨今では,多くのプレイヤーがPCI-Express Gen.4環境の素晴らしさを実感するはずである」と自信ありげに述べていた。

最後に,Hallock氏にいくつかの質問をぶつけてみたのでそのやり取りを示して終わりとしたい。

まず聞いたのは,12コア24スレッドのRyzen 7 3900Xの2つのZen 2コア(CPUダイ)の実動コアのコンフィギュレーションについてだ。基調講演レポートでは筆者は,6+6コアのほかのコンフィギュレーションもありえると記したが,Hallock氏は「6+6コアの構成のみである」と断言してくれた。

便乗して7+7の14コア28スレッドモデルや8+8の16コア32スレッドモデルがないのはなぜか,という質問に対しては「そうしたモデルの登場があるかないかについては肯定も否定もしない。ノーコメント」というお決まりの返答であった。

それと,PCI-Express Gen.4に組み込まれると言われているCPUとGPUのキャッシュコヒーレンシを取る仕組み「CCIX:Cache Coherent Interconnect for Accelerators」に関するサポート状況,もっと具体的にいえば「次世代RadeonでPCI-Express Gen.4対応のNaviと,第3世代Ryzen 3000シリーズを組み合わせたときにCCIXが有効化されるのか」について聞いてみたのだが,これは改めて返答したいとのことだった。このあたりはNaviの技術説明会などで明らかになるのかもしれない。

COMPUTEX TAIPEI 2019取材記事一覧

- 関連タイトル:

Ryzen(Zen 2)

Ryzen(Zen 2) - この記事のURL: